# Patch-Clamp Microchip Testing Circuit Interface Design Document

Team: sdmay18-10 Client: Dr. Que Long, ISU EcpE Department Advisor: Dr. Que Long Team Members: Li Qian, Team Leader Ningyuan Zhang, Programmer, Subleader Junhua Hu, Designer Chenhang Xu, Communication Leader Yigao Li, Test Leader Daiyuan Ding, Webmaster

Team Email: <u>xch@iastate.edu</u> Team Website: <u>http://sdmay18-10.sd.ece.iastate.edu/</u> Revised: 11/09/2017, Ver. 2.0

# **Table of Contents**

| 1 Introduction .                |                                        | 2  |

|---------------------------------|----------------------------------------|----|

| 1.1                             | Acknowledgement.                       | 2  |

| 1.2                             | Problem and Project Statement.         | 2  |

| 1.3                             | Operational Enviroment.                | 2  |

| 1.4                             | Intended Users and uses.               | 2  |

| 1.5                             | Assumptions and Limitations.           | 3  |

| 1.6                             | Expected End Product and Deliverables. | 3  |

| 2. Specifications and Analysis. |                                        | 4  |

| 2.1                             | Design Specifications.                 | 4  |

| 2.2                             | Proposed Design.                       | 4  |

| 2.3                             | Design Analysis.                       | 6  |

| 2.4                             | Process Details.                       | 7  |

| 3. Testing and Implementation.  |                                        | 8  |

| 3.1                             | Interface Specifications.              | 8  |

| 3.2                             | Hardware and software.                 | 9  |

| 3.3                             | Functional Testing.                    | 10 |

| 3.4                             | Non-functional Testing.                | 10 |

| 3.5                             | Modeling and Simulation.               | 11 |

| 3.6                             | Implementation Issues and Challenges.  | 11 |

| 3.7                             | Technical Approach.                    | 11 |

| 3.8                             | Results.                               | 11 |

| 4 Closing Material              |                                        | 11 |

| 4.1                             | Conclusion.                            | 11 |

| 4.2                             | References.                            | 12 |

List of Graphs:

graph 2.2.1: Implementation block diagram

graph 2.3.1: microchip setup

graph 3.2.1: PC-ONE Whole Cell Patch-Clamp

graph 3.2.2: Oscilloscope

graph 3.2.3: Function Generator

graph 3.2.4: Micro Chip

# **1** Introduction

#### 1.1 Acknowledgement

This design document was supported by our advisor Dr. Que Long and graduated student Silu Feng. We thank them for their great assistance in this project, although they may not agree with all of the interpretations of this design document.

#### 1.2 Problem and Project Statement

Patch-clamp is a technology in biological engineering field which means to catch cell with tiny clamp and observe the bioelectricity behavior of the cell. Our project is focusing on how to build up a set of electric environment and circuit to provide operational interface between the patch-clamp and electron microscope. With patch-clamp, human will observe a clearer picture about cells, which for our project are neurons, the nerve system cells. This could be done with getting a clear electric current square graph of the currents that generated when ions try to enter and leave the membrane of neurons, and this is what we do for our project to build the interface to capture the current graph. These behaviors of neurons will lead biological engineers to look for many possible cures of some serious nerve diseases that could not be cured right now.

We use PC-ONE Patch/Whole Cell Clamp to build the interface. This clamp equipment is also the main tool we use to build our interface.

#### 1.3 operational Enviroment

The operational environment of Patch-Clamp Microchip Testing Circuit Interface is biological laboratory with complete safety equipments and professional operators. The operation of Patch-Clamp Microchip Testing Circuit Interface must be done safely under required professional assistance.

#### 1.4 Intended Users and uses

Patch-clamp technique can not only be used in neuroscience but also a huge variety of physiological questions. For this technique is still the laboratory technique, so the user for this technique should be the experimenters, who want to know the ion current on the membrane when we apply different voltage or we use different solution in the bath. The most commonly use for this technique is drug discovery. For our project, we will test the different voltage on the neuronal cells to find the way to increase cell viability and make the neuronal cells can split fast. The method can be used on depression treatment, for we can make their neuronal cell more excited than before.

# 1.5 Assumptions and Limitations

#### Assumptions:

- The patch-clamp testing circuit can catch two cells at the same time to decrease the testing times.

- The simulation result will be useful to defeat depression .

- The mode can be used multiple times until we finish the project.

#### Limitations:

- Two semesters to work on this project

- Do not have too much testing samples (neuronal cells). We may fail many times, so it is hard to get the correct answer.

- Do not have appropriate metrial to reduce the room noise

# 1.6 Expected End Product and Deliverables

At the end of this semester, we are supposed to deliver a fully setted up patch-clamp circuit, which is operational to catch cells and observe the bioelectricity behavior of the cell. The goal is to build up a set of electric environment and circuit to provide operational and functional interface between the patch-clamp and electron microscope. In addition, before April 2018, we are supposed to measure the ion channel potential of cells

and the action potential of cells under external stimulations successful by using the patch-clamp microchip.

# 2. Specifications and Analysis

#### 2.1 Design Specifications

For our project, we need to use PC-ONE patch-lamp to setup an interface that could observe the electric current through neuron's membrane. To do so, we need a cell module, PC-ONE patch-clamp, headstage of PC-ONE, a peak-to-peak 6V power supply, and an oscilloscope. We have finished the speed test and voltage clamp test. We use the function generator to simulate the condition that when the patch attached on the membrane of neuron and recording.

We are available to get accurate data from the measurements and collecting two cells' data at the same time if we build up the experimental environment, the corresponding microchip and all of them functions correctly. Meanwhile, technically, we are going to have less noise than the normal patch clamp technique after we figure out how to reduce the noise. When Patch recording, vibration and electrode movement problems are even more of a source of noise than it is with conventional microelectrode recording setups. Microphonic noise is generated whenever motion such as a vibration due to machinery, touching the preparation area, nearby walking, and even loud speech occur near the PC-ONE Headstage and pipette holder. The vibration causes small changes in the capacitances associated with the pipette holder and Headstage input circuitry. This results in creating corresponding currents that add to the noise currents generated in the feedback resistor and the amplifier located in the Headstage.

#### 2.2 Proposed Design

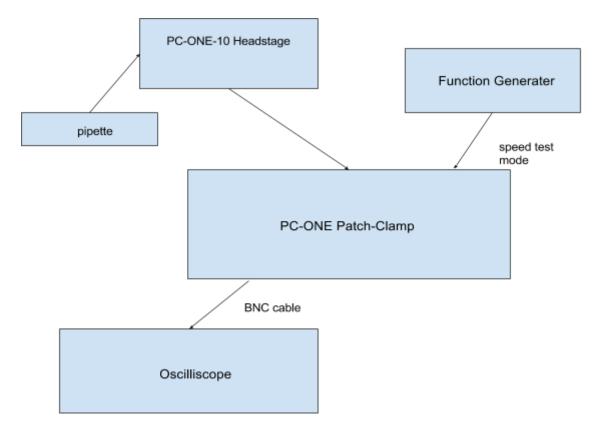

The connection of each components will be shown below as block graphs:

graph 2.2.1: Implementation block diagram

Basically, for speed test, we will use the function generator to give an simulated voltage to neuron in the cell module. This should be done without function generator. Then, we will connect headstage to PC-ONE, and another head of it to the electrode that attached on the membrane of neuron. After that, we have to setup the testing parameters on PC-ONE, which is also the most important step to get the accurate result reading of oscilloscope. The correct parameters will give a signal which will be output through the BNC cable that connected between PC-ONE and oscilloscope. Then, we could get the current graph generated when electrons enter or leave the membrane of neuron through the connected oscilloscope.

#### **Functional requirements:**

- Patch-clamp could catch neuron.

- Current could be observed through PC-ONE interface.

- Neuron must be alive during operation.

- Noise should be reduced to an acceptable range.

• When we connect every parts together, everything should work well without error

#### Non-functional requirments:

- We need to strictly follow the equipment manual to operate all operations to fulfill the project requirements.

- We have to strictly follow the safety guide of labolarity to make the experiment process safely.

- We have to cite every sources we used during the development, and ensure that the project is totally independent.

- Plan regular meeting with client to make sure the project is meeting the requirement.

- Timely maintain the project to avoid critical bugs.

- Refresh reports and document on time to meet current process.

- For ethics rules, we need to follow IEEE ethics code.

# 2.3 Design Analysis

We read the manual and document of patch clamp, tried to set up the patch clamp, and helped the graduate to make the cell model, which is also called microchip. The microchip is a glass made square chip that has four holes to let the two pipettes and silver electrodes insert, so we can catch two cells at one time, which can help us get two measured results at one testing.

The method we used to build up the interface indicated above is working relative with expected result graph when we test PC-ONE with speed test and whole cell test. The only weakness of our prototype is we still could not test it with actual neuron cell because of the settings that we are still seeking.

The observation from speed test shows that the voltage inputs from function generator seems to be too big for the capability of PC-ONE-10 Headstage, and we still need to adjust the value of input voltage and the capacitance/gains of PC-ONE to get the most accurate data.

From Whole Cell test, we see that the room noise is a big impact towards the result, and we need to find out a relative ideal way to reduce the noise generated from the PC-ONE-10 Headstage.

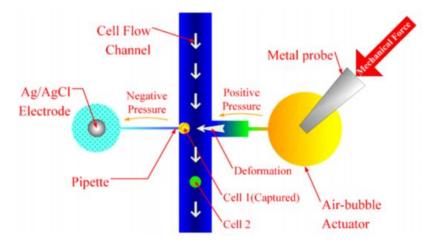

The microchip, we design for our project is lateral cell trapping. The reason for us to design this kind of microchip is we can observe the process of catching cell under the microscope. The air bubble actuator is designed for cell selection, which can generate the positive pressure(air pressure) once the target cell is observed. The electrode is made by Ag/AgCl and it has the pipette size of 3\*3 um, the resistor for it is about 1M ohms. The frabrication process of this chip is start with a silicon wafer. A 3\*3\*15 um mold of the pipette is first patterned and formed in a silicon wafer using RIE process. The size of the microchamber is 400 um in diameter and 50 um in height, which is designed for air bubble actuator.

graph 2.3.1: microchip setup

#### 2.4 Process Details

#### General Tests/Whole Cell mode:

- 1. Connect oscilloscope input port with PC-ONE FILTERED Im port located on the front panel by BNC-to-BNC cable

- 2. Connect PC-ONE-10 Headstage to PC-ONE HEADSTAGE connector

- 3. Plug a BNC-to-probe cable to the other side of PC-ONE-10 Headstage

- 4. Install pipette and silver electrode onto the microchip

- 5. Connect the probe to the silver electrode

- 6. Insert neuron with solution to the cell flow of microchip

- 7. Apply positive voltage to the electrode and negative voltage to the pipette

- 8. Pipette catch the neuron

- 9. Turn on the power of oscilloscope

- 10. Turn on the power of PC-ONE

- 11. Setup peremeters on PC-ONE

- 12. Observe the results shown on oscilloscope

- 13. Calculate the current from the generated graph

#### **Speed Test Simulation:**

- 1. Connect oscilloscope input port with PC-ONE FILTERED Im port located on the front panel by BNC-to-BNC cable

- 2. Connect PC-ONE-10 Headstage to PC-ONE HEADSTAGE connector

- 3. Connect the Function Generator output to the SPEED TEST BNC connector at the back of PC-ONE with BNC to BNC cable

- 4. Turn on the power of oscilloscope

- 5. Turn on the power of PC-ONE

- 6. Turn on the power of function generator and set a 6V peak-to-peak AC signal with Ramp shape wave and period of 10 ms

- 7. Setup peremeters on PC-ONE

- 8. Turn on the output switch on function generator

- 9. Observe the results shown on oscilloscope

# **3 Testing and Implementation**

## 3.1 Interface Specifications

In our project, we need to use PC-one patch/whole cell clamp.

We are going to use PC-ONE Whole Cell Patch-Clamp to get the signal from PC-ONE-10 Headstage and amplify the signal so we could output it to the oscilloscope. The pipette with micro chip is also required to connect with headstage so we could use headstage to process the signal from the probe connected with the silver electrode that is inserted inside the membrane of the neuron. Neuron will be put into solution and flow through the cell flow located on the microchip. The oscilloscope will catch the output from PC-ONE to generate the voltage graph we are wanting.

## 3.2 Hardware and software

The hardware we will use for our project is PC-ONE whole cell patch, whose main job is amplifying the signal generated by headstage. The function generator will generate the voltage for the real simulation in speed test. The microchip will be fabricated for the cell select. And we also need the electrode to give the positive and negative voltage to catch the cell.

graph 3.2.1: PC-ONE Whole Cell Patch-Clamp

graph 3.2.2: Oscilloscope

graph 3.2.4: Micro Chip

# Software used:

graph 3.2.3: Function Generator

There is no software used for our project, we will record the data manually.

## 3.3 Functional Testing

For this part, we have done two functional tests in this semester, which are "Whole Cell" mode test and "Speed Test" mode test.

#### Voltage clamp test

To make sure the voltage clamp is work well in our laboratory. We will test the PC-ONE in voltage clamp mode. The result we get from the oscilloscope should be o volt with about 3~5 mV white noise ride on it. The result we got right now is about 15~20 mV for there are some room noise we cannot avoid.

#### Speed Test

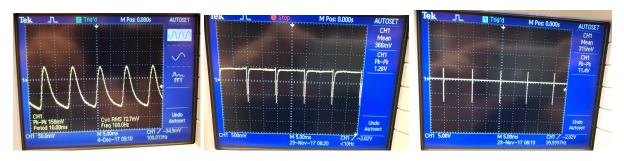

We also need to do the speed test, which is the real simulation. We will use function generator to replace the cell in the whole circuit. The voltage we given is 6V peak to peak. The headstage we choose to use this time is PC-ONE 10 (10M ohms), which is designed for the large whole cell test. The result we get from the test is about 300 mV in amplitude with a period of 10 msec square wave. The headstage should be covered with a BNC cap to reduce the noise. We use the aluminum foil to block the room power noise. But the electrical noise generated by the computer and microscope cannot be avoided this time. In this case, the result we got is quite different from the standard, which is 150 mV in amplitude.

#### Tests with Neuron Involved

This part is what we are going to finish for the second semester. We will let the actual neuron flow into the microchip with solution and plug all pipettes and electrodes to the microchip and connect it to the headstage to start data collection.

# 3.4 Non-functional Testing

For non-functional test, We followed every possible instructions from the equipments' manual and obey every safety guide of lab. We did a lot of researches according to the PC-ONE patch-clamp, include contacting DAGAN, the company produced this device to approach the most possible accurate setting of PC-ONE. All resources we used in our documents, reports and plans are well cited.

# 3.5 Modeling and Simulation

Based on our research, we were using speed test to run the simulation. However, the hardware that used on the test of the model is not same as what we used. Therefore, we needed to figure out another way to set up the equipment, in order to get the correct result.

# 3.6 Implementation Issues and Challenges

#### **Challenges:**

- Reduce the noise that influence the final results

- Find the proper solusion/inoculum for the neurons

- Find the proper material for electrodes

- Keep the cell alive during the test

- Lack of background knowledge

#### **Issues:**

- PC-ONE-10 is not the preffered headstage for our projects

- The settings' paremeters on PC-ONE to fit PC-ONE-10 will require us to figure out by ourselves

# 3.7 Technical Approach

- Use PC-ONE equipment to catch the neuron

- Inject proper voltage to the neuron to the cell

- Amplify the electron moving by microchip, enlarge the result so that we could obtain in the oscilloscope

- Reduce the noise of the projection, keep trace of electron moving clearly

## 3.8 Results

#### graph 3.8.1: Waveforms of speed tests

Above three waveforms are generated through the speed tests when we applied the 6V peak-to-peak AC ramp voltage signal through function generator to the PC-ONE to simulate the voltage applied to the neuron by electrode. In this test, we were expecting a square wave with amplitude of 150 mV, but from above three graphs we could see that the closest result is the first one which is a sine wave instead of square. This is because the PC-ONE-10 Headstage is not the most preferred headstage for the project. From the researched we have done so far, the best headstage for our project should be PC-ONE-40 which is also made by DAGAN. For this reason, we need to do more adjustments to make the PC-ONE-10 Headstage suit the project with our own parameters.

## **4 Closing Material**

#### **4.1 Conclusion**

Our project is focusing on how to build up a set of electric environment and circuit to provide operational interface between the patch-clamp and electron microscope. With patch-clamp microchip, people could observe a clearer picture about cells, which for our project are neurons, the nerve system cells. This could be done with getting a clear electric current square graph of the currents that generated when ions try to enter or leave the membrane of neurons. We are going to measure the ion channel potential of cells and the action potential of cells under external stimulations after we setting up the patch-clamp microchip successfully. Meanwhile, during the process of experimental measurements, we should figure out a method to store these neuron cells to keep them alive as well as to reduce the noise from outside environment.

## 4.2 References

[1]: IEEE Code of Ethics,

https://www.ieee.org/about/corporate/governance/p7-8.html

[2]: Y Zhao\*1, S Inayat\*1, D A Dikin\*2, J H Singer\*3, R S Ruoff\*4, and J B Troy\*1, Patch clamp technique: review of the current state of the art and potential

contributions from nanoengineering, 08 June 2009, DOI:

10.1243/17403499JNN149.

1: Department of Biomedical Engineering, Northwestern University, Evanston, Illinois, USA.

2: Department of Mechanical Engineering and Department of Physics and Astronomy, Northwestern University, Evanston, Illinois, USA.

3: Department of Ophthalmology and Department of Physiology, Northwestern University, Chicago, Illinois, USA.

4: Department of Mechanical Engineering and Texas Materials Institute, University of Texas, Austin, Texas, USA.

[3]: Zhongcheng Gong, Krithika Nagarajan, Siva Penmetsal, David Millsl, and Long Quel, A patch-clamp device with integrated actuators for cell selection and positioning, Institute for Micromanufacturing, Louisiana Tech University, USA, School of Biological Science, Louisiana Tech University, USA.

[4]: Dagan Corporation, PC-ONE Patch/Whole Cell Clamp Operating Manual Ver.1.1, www.DAGAN.com.

[5]By Winter20jb - I illusrtated this diagram on my computer, CC BY-SA 3.0, https://en.wikipedia.org/w/index.php?curid=44365802